# Implementation of Open Core Protocol transaction Verification IP using System Verilog UVM methodology

Siddaram Patil, Arun Kumar, Dr.v.Venkateswarlu

**Abstract** - This paper presents Implementation of the Reusable Open Core protocol (OCP) transaction Verification IP (VIP) using universal verification methodology (UVM) and very easy to implement the functional coverage and SystemVerilog assertions (SVA) using powerful System Verilog (SV) Language. As verification of the design has become most challenging task, verification is important factor for achieving time to market (TTM) of the product. This paper address briefly on how the UVM methodology and SV enables developing VIP easier and quickly over traditional Hardware description language(HDL) verilog or VHDL and Hardware verification language(HVL) Specman.

#### Keywords:

OCP, SV, UVM, SVA, VIP, SOC, TTM, HDL, OOPS

# I. APPLICATION OF SV AND UVM IN OCP VIP.

The Current VLSI industry is moving rapidly in adapting the feature of SV and UVM in their IP and SOC level verification because of its strong advantages over the traditional HDL language like Verilog or VHDL and HVL language specman.

As the system Verilog is developed based on OOP's (object oriented programming) concepts and superset of Verilog, the environment can be extended and add new features without affecting the original existing code. SV supports constrained randomization, assertion and functional coverage.

UVM methodology reduces the time to develop VIP by using already built in base classes for all the required components from the UVM library and also helps re-using the VIP environment at different level of abstraction i.e. at module level and chip level.

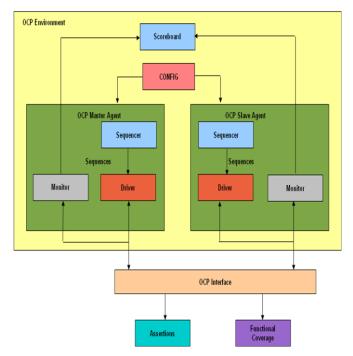

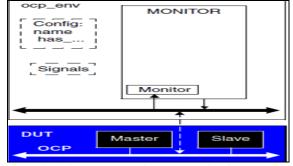

Arun kumar, Professor, VTU Extension Centre, UTL Technologies Bangalore -22, Karnataka, India, arunkumar@utltraining.com Application of SV in OCP VIP is that, the SV interface construct is used for communicating class based environment to module based environment and creating array of physical interface which helps in generating multiple OCP master/ slave VIP interface without much effort. SV constructs cover group, cover point and covergroup.sample is used for achieving functional coverage. SV construct property and assert is used for assertion coverage. The interface, functional coverage and assertion blocks shown separately in fig 1

Application of UVM in OCP VIP is that, the UVM built in base class for different components are used from the UVM library to develop OCP VIP such as, uvm\_env class to build the environment, uvm\_test class to develop the tests, uvm\_sequence\_item class to build properties of base tests, uvm\_sequence class to develop the different test scenario, uvm\_driver to generate the transactions to DUT for OCP\_master/ slave driver, uvm\_monitor to sample the activity of OCP bus

OCP VIP utilized other features of UVM like uvm\_config\_db::set to configure the physical interfaces or array of physical interface to different components in the environment such as OCP master/ slave agents, master/ slave driver, master/ slave sequence. UVM IS\_ACTIVE feature can be used to make the OCP\_VIP agent as active or passive based on value of IS\_ACTIVE bit, this feature enables the OCP VIP agent to contain driver, sequencer and monitor if UVM IS\_ACTIVE is set otherwise only monitor is enabled. Different OCP components are shown in fig 1.

Siddaram Patil, M Tech, Final Semester VLSI Design and Embedded Systems, VTU Extension Centre, UTL Technologies Bangalore -22, Karnataka, India. srpatilsedam @gmail.com

#### **II. INTRODUCTION**

Open core transaction protocol is data/signal communication protocol in on chip core interfaces or in SOC. OCP data communication models range from simple request grant handshaking through pipelined request – response to complex out –of order transaction.

OCP describes a point-to- point interface between two communication module, such as IP cores and bus interface modules(bus wrappers)[1].in SOC the more number of IP core behavior, performance and interface requirements, a standard fixed definition interface protocol cannot address the all the system interface requirements. The need to support test requirement and verification adds a more complexity to the interface. To address the all system interface requirement, OCP defines a highly flexible and configurable interface.

As OCP makes IP modules independent of integration environment and interconnection technology, helps in reuse of OCP complaint modules in multiple SOC products.

The OCP VIP is a ready-made, highly configurable UVM verification environment, suitable for design under test (DUT) with an OCP interface. The OCP VIP can generate stimuli in an OCP bus format (single and burst), execute traffic over a bus as an OCP master to a DUT slave. Respond, as an OCP slave, to traffic coming from a DUT master. Ensure that the DUT adheres to OCP protocol rules, collect bus traffic and DUT behaviour information, according to OCP coverage items, all UVC behaviour is in accordance with the OCP 3.0 Specification.

The paper is organized as follows: section III describes the OCP VIP architecture. The Basic OCP signal description table in section IV. Flow Charts for master slave interaction and basic write read in section V. Implementation of assertion and functional coverage in VI. Typical application of OCP VIP in VII. The simulation results are presented in section VIII. Re-using of OCP VIP to generate multiple OCP master and slave interfaces in VIII and the conclusion is arrived at section XI.

# III. OCP VIP Architecture in System Verilog UVM

The above fig 1 shows the OCP VIP architecture using System Verilog UVM methodology, it contains master and slave agents are instantiated in the OCP environment. Each master and slave agent contains its own monitor, Sequencer and driver respectively.

OCP Agent can be configured as Passive or active based on the requirement. The configuration can specify the agent as passive, which disables the creation of sequencer and driver. OCP configuration decides the how the OCP environment should function.

Fig 1 OCP verification IP architecture block diagram

The OCP Sequencer supports Generating and driving bus traffic as an OCP master. The UVC emulates the full behaviour of an unlimited number of OCP masters capable of generating all types of OCP transfers. Responding to bus traffic as an OCP slave. The UVC emulates the full behaviour of an unlimited number of OCP slaves that respond to traffic over a bus and generates all types of responses to a DUT master.

The OCP Driver support all OCP protocol data and address widths, OCP protocol burst transfers like continues READ and continues WRITE and assertions and checks for protocol violations.

The OCP monitor operates in three different modes: Bus Monitor, Master Monitor and Slave Monitor. By default Bus Monitor is active all the time in OCP environment. The UVC logs the bus traffic for the purpose of debugging its elements and DUT devices. Provides option for data integrity check, coverage collection. Supports all OCP Single, Burst, Tags and Treads Operations and all the commands.

OCP Scoreboard takes transaction packets from master monitor and slave monitor and compares both of them, two queues of packets are implemented in the scoreboard in order to receive the packets from both the monitors and store them temporarily. As soon as both the queues become non-empty, one packet from each of the queues is pulled out and compared. If a mismatch occurs, error is given out.

| Name        | Width       | Driver | Function      |

|-------------|-------------|--------|---------------|

| CLK         | 1           | Varies | Clock input   |

| MAddr       | Configurabl | Master | Address       |

|             | e           |        |               |

| MCmd        | 3           | Master | Command       |

| MData       | Configurabl | Master | Write data    |

|             | e           |        |               |

| MDataValid  | 1           | Master | Write data    |

|             |             |        | valid         |

| MRespAccept | 1           | Master | Master        |

|             |             |        | accepts       |

|             |             |        | response      |

| SCmdAccept  | 1           | Slave  | Slave accepts |

|             |             |        | transfer      |

| SDataAccept | 1           | Slave  | Slave accepts |

|             |             |        | write         |

|             |             |        | data          |

| SData       | Configurabl | Slave  | Read data     |

|             | e           |        |               |

| SResp       | 2           | Slave  | Transfer      |

|             |             |        | response      |

**IV. BASIC OCP SIGNAL DESCRIPTION [11]**

Table 1 Basic OCP signals

# V. FLOW CHARTS

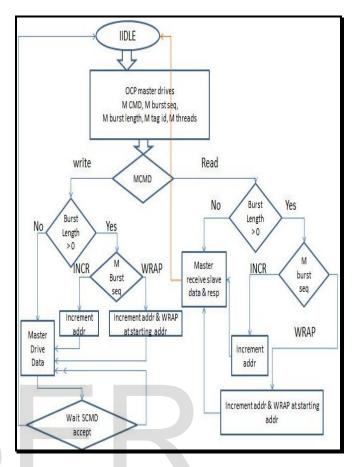

#### A. Master and Slave interaction Flow

This Flow chart explains how the master drives stimulus to slave, how slave responds for the master commands. Shows the monitors and scoreboard with test status PASS or FAIL.

## B. OCP Write and Read Flow

# VI. ASSERTION and FUNCTIONAL COVERAGE

# A. Assertion [3] [11]

System Verilog Assertion helps in checking the behaviour of the code and it can be reused across the project without many difficulties. We can instantiate the assertion code in the test bench using "bind" command that will bind the assertion module ports to the DUT ports. Even we can insert the assertion in the interface. If you know the ports signals of modules, one can easily write the assertion logic independently without any dependency. Assertions also called as control oriented coverage

**Example:** when the SCmdAccept is low and transfer is not IDLE the Master should hold the data until the SCmdAccept is high. (Need to constraint the number of clock cycles to hold the data)

assert property (p1) else  $error("ASSERTION ERR:MAddr is not stable incase of SCmdAccept is low and transfer is not IDLE\ n\ n");$ endmodule

### B. Functional Coverage [2] [11]

Functional Coverage used to measure how effectively The VIP tested all the feature of design, functional coverage also called data oriented coverage.

#### Example:

class ocp\_bus\_monitor extends svm\_monitor #(ocp\_master\_basic\_sequence\_item,ocp\_slave\_packet); /-OCPFunctional Coverage groups Declarations

```

covergroup ocp_cov;

option.per_instance = 1;

transTypes1: coverpoint intf.MBlockHeight {

ignore_bins Low = \{0, 1\};

bins High = \{2,3\};\}

transTypes2: coverpoint intf.MBurstLength {

bins MBurstLength_2 = \{2\};

bins MBurstLength_4 = \{4\};

bins MBurstLength_8 = \{8\};

bins MBurstLength_{16} = \{16\};

bins MBurstLength_{32} = \{32\};

bins MBurstLength 64 = \{64\};

transTypes3:coverpoint intf.MBurstSingleReq;

transTypes4:coverpoint intf.MCmd;

endclass

```

# VII. TYPICAL APPLICATION OF OCP VIP

OCP VIP used to perform DUT verification at the block level or chip level. These features are enabled by configuration file.

#### A. Block-Level DUT Verification

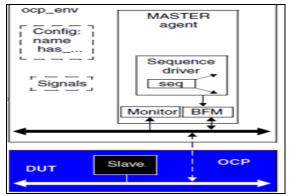

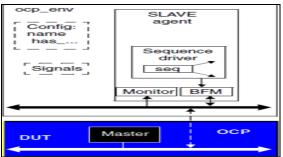

The OCP VIP is typically used to verify individual bus agents, such as bus masters or bus slaves. Figure 2 and Figure 3 depicts typical applications of the VIP at block level.

Figure 2 OCP VIP as Master-Testing a Single DUT Slave

Figure 3 OCP VIP as Slave- Testing a Single DUT Master

#### B. Chip-Level DUT Verification

OCP Monitor can be used to monitor a DUT with Master and Slave. Figure 4 depict typical application of Bus monitor or Master monitor or Slave monitor

Figure 4 OCP Bus monitors- Monitoring a DUT with Master and Slave

# **VIII. SIMULATION RESULTS**

#### A. OCP BASIC TRANSACTION WAVEFORM I. Read transfer

Wrap burst write

II.

| Name                       | ¢۳ | Cursor  | ¢۳   | 0     | 500ns    | 1000ns | 1500 | ns    | 2000 | Ons  | 25    |

|----------------------------|----|---------|------|-------|----------|--------|------|-------|------|------|-------|

| <b></b> / Clk              |    | 1       |      |       |          |        |      | תתתת  | MN   |      | NNNL  |

| ⊕ <sup>4</sup> MAddr [7:0] |    | 'h 90   |      | хх    | 00       |        |      | 94    | 98   | 9C   | 90 () |

| 🗄 📲 📠 MData(31:0)          |    | 'h 16F0 | CAGE | хххх▶ | 00000000 |        |      | 16F0) | 1    | 16F) | 16)   |

| ⊕ 📲 MBurstLength(8:0)      |    | 'h 004  |      | ххх   | 000      |        |      | 004   |      |      |       |

| ⊕¶an MBurstSeq[2:0]        |    | 'h 2    |      | x     | 0        |        |      | 2     |      |      |       |

|                            |    | 1       |      |       |          |        |      |       |      |      |       |

| ⊕¶a MCmd[2:0]              |    | 'h 1    |      | х     | 0        |        |      | 1     |      |      |       |

| MReqLast                   |    | 1       |      |       |          |        |      |       |      |      |       |

|                            |    | 0       |      |       |          |        |      |       | П    |      | LL    |

|                            |    | 0       |      |       |          |        |      |       |      |      |       |

| ⊕ <b>_√</b> SResp[1:0]     |    | 'h O    |      | x     | 0        |        |      |       |      |      |       |

IJSER © 2014 http://www.ijser.org

#### Instance (default scope): 🧃 uvm\_pkg 🕨 🧃 uvm\_test\_top 🕨 🧃 env 🕨 🧃 m\_agnts(0) 🕨 👔 monl Overall Local Grade: 🗾 2 100% | Functional Local Grade: 🔜 100% | CoverGroup Local Grade: 🗾 100% | Assertion Local Grade: 👘 🖉 Edit. 💡 Cover Groups (100%) 👔 COVER GROUPS ♦ 🗸 🛛 🛛 BINS OF: 🗳 transTypes2 0 × 0 H Name Overall Average Grade Overall Covered Overall Average Grade Overall Covered 100% 48/48(100%) ≗ MBurstLength 4 100% 1/1(100%) 81 MBurstLength\_B 100% 171 (100%) - MBurstLength\_16 100% 1/1(100%) 171 MBurstLength 32 100% 1/1(100%) 811 1/1(100%) MBurstLength\_6 100% Details of: 🗳 transTypes2 Source butes itor.sv (out of sync) 🛛 🛚 uvm\_pkg.sv × ocp\_mo 0 D ignore\_bins Low = { bins High = {2.3}:} Overall Overall Covered birs High = {2,3};} point inf /Burstlangth { birs Menstlangth 2 = {2}; birs Menstlangth 2 = {2}; birs Menstlangth [4 = {4}; birs Menstlangth [6 = {16}; birs Menstlangth 2 = {32}; birs Menstlangth 3 = {42}; birs Menstlangth 6 = {64}; point inf /Menstlangth 6 = {64}; 100% 1/1(100%) 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 🔓 transTypes3 100% 2 / 2 (100%) transTypes4 100% 8/8(100%) transTargets. 3/3(100% transTypes3:coverpoint intf.MBurs transTypes4:coverpoint intf.MCnd; transResults1 100% 4/4 (100%) transBurstProps 100% 1/1(100%) transBurstProps 100% 2/2(100%) 🔓 transBurstProps3 100% 3/3(100%) 🖕 flowThreads1 🍟 flowThreads2 100% 2/2(100%) 100% 1/1(100%) alts]:coverpoint intf.SResp rstPropsl:coverpoint intf.MAtomicLength { flowThreads3 100% 1/1(100%) bins atomiclength = {1,2};} Props2:coverpoint intf.MEurstPrecise Props3:coverpoint intf.MEurstSeq { flowTagTypes \_\_\_\_ 2/2(100%) 100% 🔓 flowTagTypes2 2/2(100%) flowTapTypesS 100% 2/2(100%) bins incr = {0}; bins wrap = {2}; bins dblock = {7}; } flowTagTypes 100% 1/1(100%) 🔓 flowTagTypes5 100% 2/2(100%) 100% INB transTypesXtransTargets 3/3(100%) Q Match Case 25 itoms

#### **B. FUNCTIONAL COVERAGE REPORT**

#### C. ASSERTION COVERAGE REPORT

| Overall Local Grade: 🗾 🛛 1009      | Functional Local Grade: 💼 | 2 300% CoverGroup Loca | al Grade: n/a   J | lasertion Local Grade: 200%                         |                                                |  |

|------------------------------------|---------------------------|------------------------|-------------------|-----------------------------------------------------|------------------------------------------------|--|

| Circ Olick to edit attributes Asse | ertions (100%)            |                        |                   |                                                     |                                                |  |

| SSERTIONS                          |                           |                        | • D Sour          | ne af: 🤌 p94                                        |                                                |  |

| Name                               | Overall Average Grade     | Status                 | ocp               | signallevelassertions.sv (out of sync) 🛛 🛔          |                                                |  |

| (no fibe)                          | (no fiber)                | (no fiber)             | 16                | 7                                                   |                                                |  |

| 2 254                              | 1025                      | Passed                 | <b>1</b> 6        |                                                     |                                                |  |

| <b>№</b> 256                       | 100%                      | Passed                 | 16                |                                                     |                                                |  |

| N 95                               | ✓ 100%                    | Passed                 | - 1 iz            |                                                     | flag burst == 1    ccp vif.cfg idla reg == 1 ) |  |

| N reset assertion                  | 2 102%                    | Passed                 | 17                |                                                     |                                                |  |

| 📢 pl                               | 2 102%                    | Passed                 | 37                |                                                     |                                                |  |

| <b>№</b> \$2                       | 100%                      | Passed                 | 17                | # ##0 ccp_vif.MRxpLast == 1;<br>5 endproperty       |                                                |  |

| Fa 📢                               | 2 100%                    | Passed                 | 12                |                                                     |                                                |  |

| N 14                               | 2 109%                    | Passed                 | 17                |                                                     |                                                |  |

| 😥 p5                               | <ul> <li>1095</li> </ul>  | Passed                 | 17                |                                                     | in the last transfer of the burst");           |  |

| 💫 ឆ្នាំ                            | ✓ 1095                    | Passed                 | = 17              |                                                     |                                                |  |

| N al                               | 100%                      | Passed                 | 18                |                                                     |                                                |  |

| pi pi                              | 2 109%                    | Passed                 | 18                |                                                     |                                                |  |

| 😡 p3                               | 2 100%                    | Passed                 | 18                |                                                     |                                                |  |

| pia (i)                            | 100%                      | Passed                 | 18<br>18          |                                                     |                                                |  |

| p) p11                             | 2 100%                    | Passed                 | 10                |                                                     | flag burst == 1    ccs vif.cfs idle reg == 0)  |  |

| N p12                              | 2 109%                    | Passed                 | 18                | 7 ((crt - ccp vif.Merstlangth -1) 66 (ccp vif.cfg i | (la rej 1))                                    |  |

| N p13                              | 2 100%                    | Passed                 | 18                |                                                     |                                                |  |

| <b>€</b> \$24                      | 1095                      | Passed                 |                   | 4                                                   |                                                |  |

| N p25                              | ₹ 1095                    | Passed                 | Q                 | ÷ ÷                                                 | Match Case                                     |  |

| N 216                              | 2 109%                    | Passed                 |                   |                                                     |                                                |  |

| ja17                               | 2 109%                    | Possed                 | Attri             | butes di 🧊 p94                                      |                                                |  |

| 10 p10                             | 100%                      | Passed                 | Col #             | Name                                                | 4 Value                                        |  |

| 120                                | 2 1095                    | Passed                 |                   | (no fiber)                                          | (no fiber)                                     |  |

| p21                                | 100%                      | Passed                 |                   | Assertion Average Grade                             | 100%                                           |  |

| € #22                              | 2 107%                    | Passed                 |                   | Assertion Covered                                   | 10                                             |  |

| p 23                               | 1095                      | Passed                 |                   | Assertion Ignored                                   | 0.0                                            |  |

| 134                                | 1005                      | Passed                 |                   | Assertion Tatal                                     | 1.0                                            |  |

| 0 025                              | 2 1025                    | Passed                 |                   | Assertion Total Weighted Coverage                   | 18                                             |  |

| ₩ 235                              | 10%                       | Passed                 |                   | Assertion Tatal Weights                             | 10                                             |  |

| € s27                              | 10%                       | Passed                 |                   | Assertion Uncovered                                 | 03                                             |  |

| ka 123                             | 10%                       | Passed                 |                   | Enclosing Entity                                    | top.U_assertions                               |  |

| 10                                 | 1095                      | Passed                 |                   | Exclusion Comment                                   |                                                |  |

| 101                                | 2 1025                    | Prosed                 | -                 | Exclusion Reviewer                                  |                                                |  |

| wiso 74 items                      |                           |                        |                   | Exclusion Rule Type                                 | Note                                           |  |

### IX. REUSE OCP VIP TO GENERATE MULTIPLE MASTER/SLAVE

Re-used the OCP VIP environment to create multiple master and multiple slave with the help of System verilog interface concepts, which is used to creates array of interface structure and also similarly UVM feature uvm\_config\_db::set method is used to assign each individual array of physical interface from the top level environment to array of master/ slave agents without any difficulties, the connections happens automatically. The above implementation can be done in simple way as shown below steps.

1. Define how many number of master or slave instance required using define NUM\_INTF, the physical OCP interface will be created NUM\_INTF times in top level module environment

`define NUM\_INTF 5 module top(); reg Clk; ocp\_interface ocp [`NUM\_INTF] (Clk); endmodule

Assigning the sequences to array of master/ slave, array created is using \* i.e. env.m\_agnts\*/ env.s\_agnts\*. if we not use array structure, then individually we need configure NUM\_INTF times(it will not be generic)

for (int k=0; k<`NUM\_INTF; k=k+1)

begin //mstr/slave

uvm\_config\_db#(uvm\_object\_wrapper)::set(this,

env.m\_agnts\*.sequencer.main\_phase", default\_sequence",

ocp\_wrap\_write\_burst\_seq::type\_id::get());

uvm\_config\_db#(uvm\_object\_wrapper):set(this,

"env.s\_agnts\*.s\_sequencer.main\_phase", "default\_sequence

", simple\_response\_seq::type\_id::get());

end</pre>

3. Connect the array of physical interface from top level to array of OCP master/slave agents components without much effort using UVM feature uvm\_config\_db::set

for ( genvar k=1; k<`NUM\_INTF; k=k+1) begin initial begin swrite(m\_agnt\_name, "\*.env.m\_agnts[%0d]", k); \$swrite(s\_agnt\_name,"\*.env.s\_agnts[%0d]", k); uvm\_config\_db#(virtual ocp\_interface)::set(null,m\_agnt\_name,"intf",top.ocp[k]); uvm\_config\_db#(virtual ocp\_interface)::set(null,s\_agnt\_name,"intf",top.ocp[k]); uvm\_config\_db#(virtual ocp\_interface)::set(null,{m\_agnt\_name,".mon1"},"intf",to p.ocp[k]: uvm\_config\_db#(virtual ocp\_interface)::set(null,{s\_agnt\_name,".s\_monitor"},"intf" ,top.ocp[k]); uvm\_config\_db#(virtual ocp\_interface)::set(null,{m\_agnt\_name,".m\_basic\_s equence\_driver"},"intf",top.ocp[k]); uvm\_config\_db#(virtual ocp\_interface)::set(null,{s\_agnt\_name,".s\_driver"},"int f",top.ocp[k]);end end

By changing only one parameter value NUM\_INTF=10, environment has created 10 OCP master/ slave interface and observed transaction on all the master/ slave interfaces.

## X. CONCLUSION

System Verilog UVM methodology verification IP provides reusable and configurable VIP at Various levels of abstractions. Verification IP of OCP allows the customer to reuse the VIP environment in their soc environment without much effort when connecting multiple master/ slave VIP if the DUT contains multiple OCP master/ slave. Usage of Powerful feature of System Verilog assertion and functional coverage gives the confidence for designer to release the products. Reusing of Verification IP of OCP helps to achieve time to market of the SOC design

#### REFERENCES

- Chih-Wea Wang, Chi-Shao Lai, Chi-Feng Wu, Shih-Arn, and Ying-His Lin, "On-Chip Interconnection Design and SoC Integration with OCP", 13 Jun 2008, VLSI Design Automation and Test (VLSI-DAT)

- [2] Shihua Zhang, Asif Iqbal Ahmed and Otmane Ait Mohamed, "A Reusable verification Framework of Open Core Protocol", Circuits and Systems and TAISA Conference, 2009, pp. 1-4, june 28, 2009

- [3] Kun Tong and Jinian Bian, "Assertion-based Performance Analysis for OCP Systems."In Proc. Circuits, Signals, and Systems (CSS 2007), Banff, Alberta, Canada, July 2007

- [4] Natale Barsotti, Riccardo Mariani, Matteo Martinelli, and Mario Pasquariello, "Dynamic verification of OCP-based SoC", in Proc. IEEE Int'l Conf. on System-on-Chip, Tampere, Finland, Nov. 2005, p. 22

- [5] Chih-Wea Wang, Chi-Shao Lai, Chi-Feng Wu, Shih-Arn Hwang, and Ying-Hsi Lin, , "On-chip Interconnection Design and SoC Integration with OCP", Proceedings of VLSI-DAT, 2008, pp. 25-28, April 2008

- [6] Chin-Yao Chang, Yi-Jiun Chang, Kuen-Jong Lee, Jen-Chieh Yeh, Shih-Yin Lin and Jui-Liang Ma, "Design of On-Chip Bus with OCP Interface", 28 Jun 2010, VLSI Design Automation and Test (VLSI-DAT)

- [7] Chien-Chun (Joe) Chou, Konstantinos Aisopos, David Lau, Yasuhiko Kurosawa and D. N. (Jay) Jayasimha, "Using OCP and Coherence Extensions to Support System-Level Cache Coherence", Technical Paper, pg. nos.10, April 2009

- [8] Bhakthavatchalu R, Deepthy G.R., Shanooja S, "Implementation of reconfigurable Open Core Protocol compliant memory system using VHDL" Industrial and Information Systems (ICIIS), 2010 International Conference, 2010, pp.213-218, July 29, 2011

- [9] OCP-IP, A SystemC OCP Transaction Level Communication Channel V2.2, 2006

- [10] Open Core Protocol (OCP) Specification, http://www.ocpip.org/home.

- [11] Open Core Protocol Specification 3.0", International Partnership, 2000- 2009 OCP-IP Association, Document Revision 1.0.

- [12] UVM Cook book http://verificationacademy.com/uvmvm/pdf?pdf=Cookbook%2FDac2011